Foreword: The Wilderness Beyond the Brain

Inside NVIDIA's Blackwell B200 chip, signals travel at the speed of light with almost no impedance. However, the moment a signal leaves the chip and enters a copper cable or optical fiber, it's like a Ferrari leaving a racetrack and driving onto a bumpy, muddy road.

This is a harsh physical world:

- Attenuation: Signals weaken within a few centimeters.

- Noise: Signals from adjacent wires can bleed over like ghosts (crosstalk).

- Latency: When tens of thousands of GPUs communicate simultaneously, data can collide at the gateway.

Without someone to tame this wilderness, even the fastest GPU is useless, as it cannot access data.

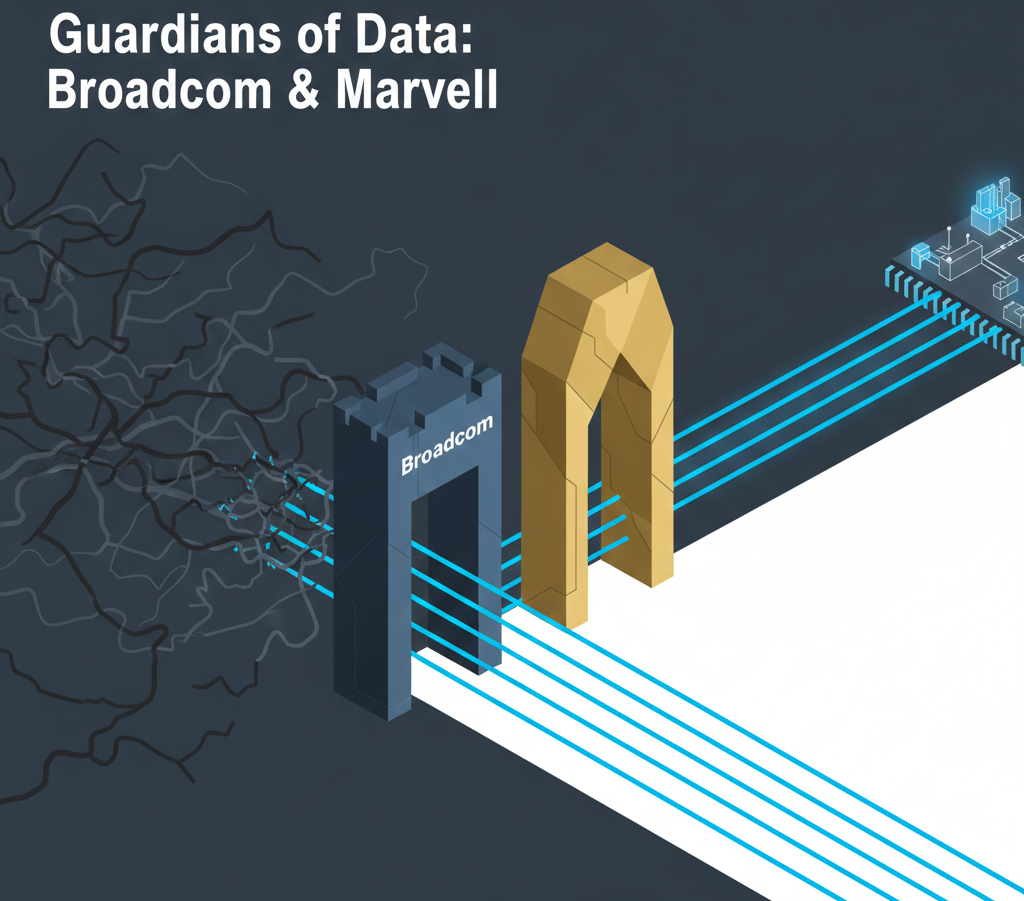

Broadcom and Marvell exist for one purpose: to combat this physical chaos and ensure data successfully reaches another chip.

🦈 Chapter One: Broadcom — The Gatekeeper of Copper

CEO Hock Tan is known as the semiconductor industry's "actuary" and "M&A king." Under his leadership, Broadcom controls 80% of global data center traffic. This means that whether you're searching on Google, streaming on Netflix, or chatting on ChatGPT, every bit of your data pays a "toll" to Broadcom.

1. Core Technology: Switch Chips — The Traffic Police of Data Centers

If GPUs are factories that produce data, then switches are the multi-level interchanges on a highway. Without them, data cannot go anywhere.

Broadcom possesses two major weapons: Tomahawk and Jericho. These two chips solve two distinctly different physical challenges.

(1) Tomahawk Series: The "High-Speed Rail Station" for Extreme Speed

Technical Specifications: The latest Tomahawk 5 offers bandwidth up to 51.2 Tbps.

Physical Challenge: How do you prevent bottlenecks when such a massive amount of data rushes in instantaneously?

Simple Analogy: A super roundabout with no traffic lights.

Imagine 51,200 Ferraris simultaneously entering a roundabout at 300 km/h, with each car knowing its exact exit and not needing to brake at all.

Tomahawk's design philosophy is "Throughput Above All." It doesn't perform complex checks (no license plate scanning, no temperature checks); its sole responsibility is to allow traffic to flow at full speed.

Strategic Importance: It serves as the spine for AI compute clusters, connecting thousands of GPUs. Outside of NVIDIA's DGX systems, almost all high-speed networks utilize it.

(2) Jericho Series: The "Logistics Center" for Stability

Technical Specifications: Features an extremely large buffer memory.

Physical Challenge: During network congestion, data packets can be lost. While this might not matter for watching YouTube (at most, the picture quality degrades), it's disastrous for AI training (lost parameters can lead to training failure and necessitate a restart).

Simple Analogy: A transfer station with a massive parking lot.

When a highway is congested, a straightforward device like Tomahawk might "kick excess cars off a cliff" (packet loss). But Jericho says, "Don't rush, I have an enormous parking lot." It temporarily stores these cars (Deep Buffer) and releases them when the path is clear.

Strategic Importance: It acts as a router for complex networks, ensuring every bit of data reaches its destination.

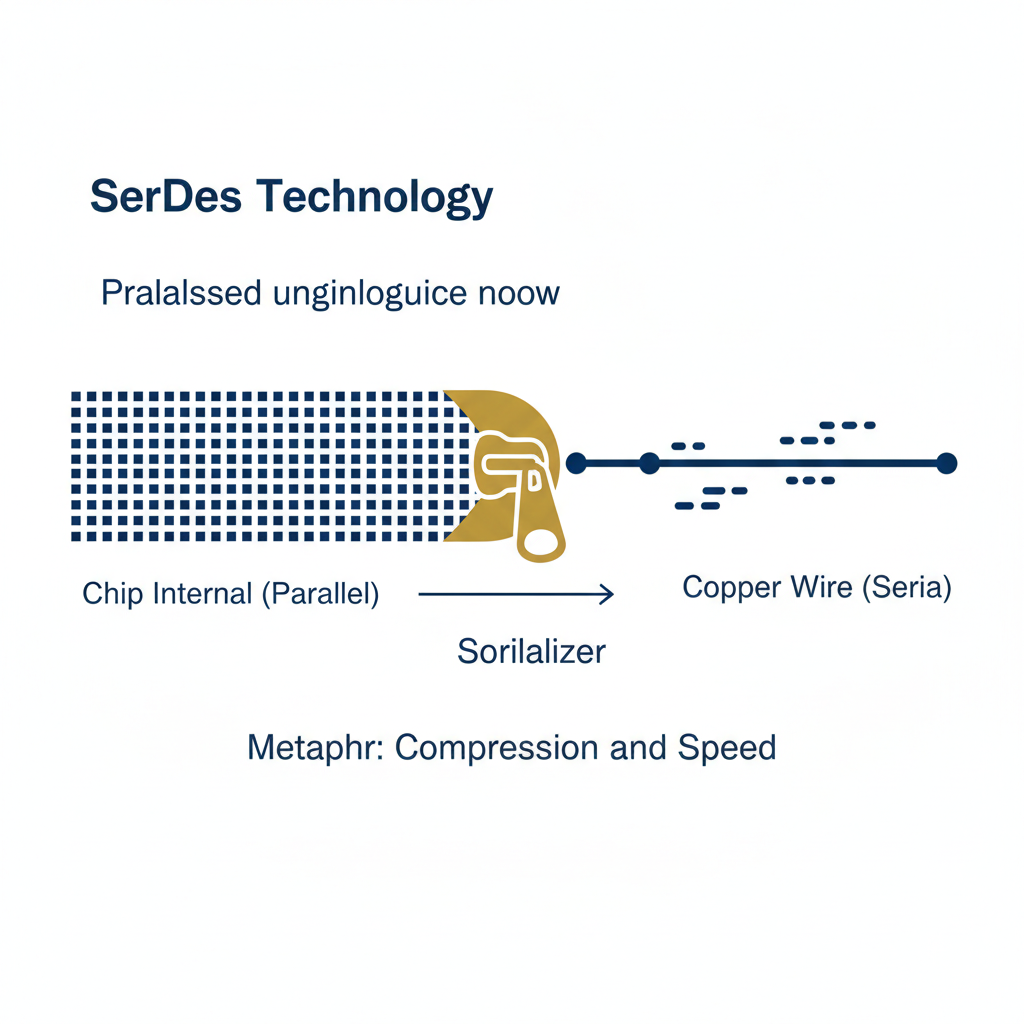

2. Deep-Dive Technology: SerDes (Serializer/Deserializer) — The "Zipper" for Digital Signals

This is arguably the most difficult-to-understand yet highest-value technology in semiconductor physics. It is also the technological holy grail that MediaTek is desperately trying to master and enter.

(1) Why is SerDes Needed?

There's a physical contradiction here:

- Inside the chip, signals prefer to "walk side-by-side": Because the pathways within the chip are wide, 1024 bits can be transmitted at once (Parallel).

- Outside the chip (cables), signals can only "walk in single file": Because cables are expensive and pins are limited, only 1 bit can be transmitted at a time (Serial).

(2) Technical Principle: Serializer / Deserializer

Simple Analogy: A magical zipper.

- Transmitter (Serializer): Like a zipper, it quickly zips together the separate teeth on both sides of a jacket (parallel data) into a single line (serial data) and sends it out.

- Receiver (Deserializer): It unzips this line, instantly restoring it to the original parallel data.

Broadcom's Dominance:

When transmission speeds reach 112G or 224G, electrons in copper wires can crash around like they're "drunk" (signal integrity issues). Broadcom's SerDes acts like a top-tier tour guide, making these "drunk" electrons line up properly, run fast, and not stumble. This is the only "mouth" for all high-speed chips (including GPUs and CPUs) to communicate externally.

(3) PAM4 Modulation — Adding "Layers" to Signals

Simple Analogy: From a switch to a dimmer.

- Traditional signals (NRZ) are like a light switch, with only "full brightness (1)" and "full darkness (0)".

- Broadcom introduced PAM4 technology, which is like a dimmer switch, offering four levels of brightness: "full darkness, dim, bright, full brightness."

This allows 2 bits (00, 01, 10, 11) to be transmitted at once. Efficiency doubles, but so does the difficulty (because distinguishing between dim and bright is challenging). Broadcom's strength lies in its ability to differentiate these levels with extreme accuracy.

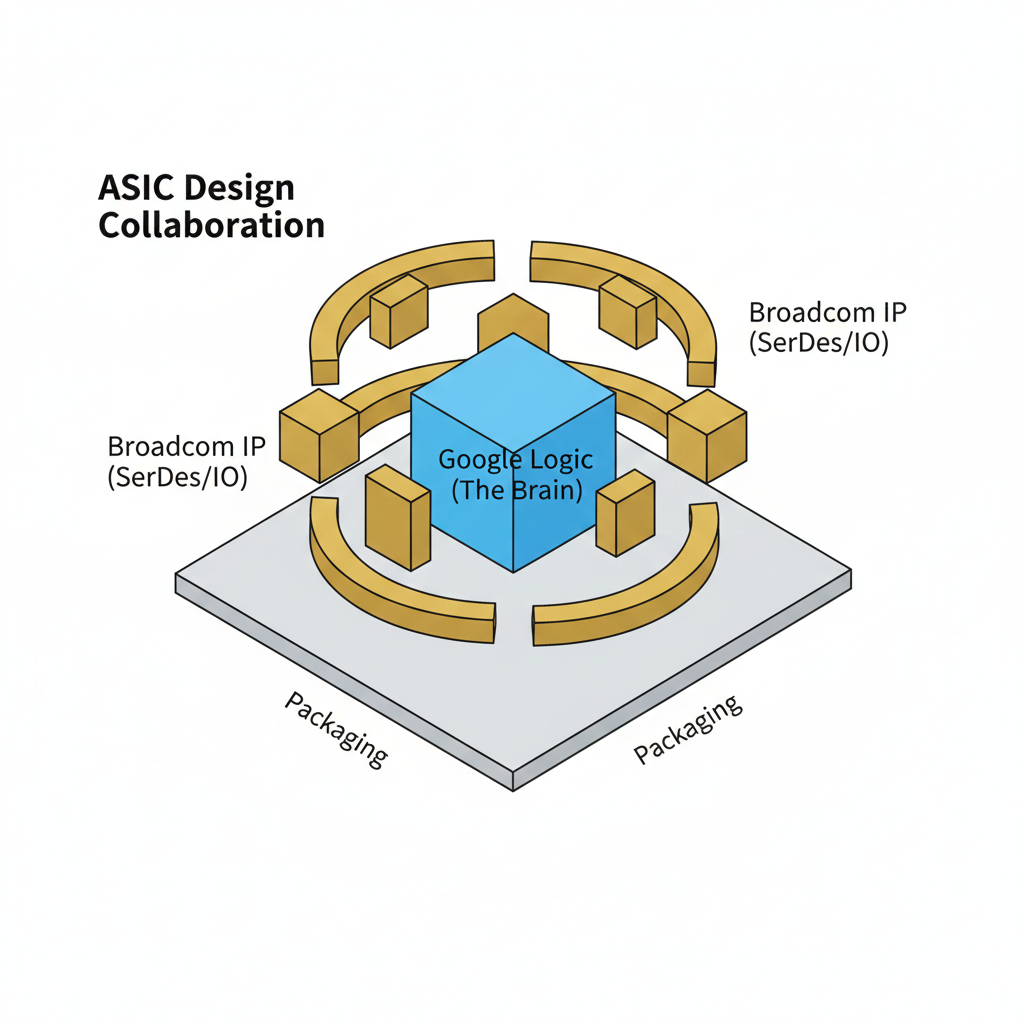

3. Cash Cow Business: ASIC (Custom Chips) — The Master Craftsman Behind Google TPU 👑

Everyone knows Google has TPUs, but few know that half of the physical circuitry in TPUs is made by Broadcom.

(1) Business Model: IP Assembly Kit

What does Google provide? "Architectural blueprints." Google's mathematicians design the matrix computation units specifically for AI, which are the brain.

What does Broadcom provide? "Plumbing, electrical wiring, and foundation." Google's compute units are islands; they need to communicate with memory (Memory Controller), with other chips (SerDes), and require packaging protection. All these peripheral circuit IPs are provided by Broadcom.

Simple Analogy: Luxury home designer vs. construction company.

Google is the designer, sketching out a beautiful living room (compute core). Broadcom is the construction company, responsible for installing the plumbing, wiring, and walls (SerDes/I/O) and physically building the house.

Key Moat: Google cannot do without Broadcom, because if they switch construction companies, the pipes might leak (slow transmission), or the house might collapse (poor yield).

⚡ Chapter Two: Marvell — The Magician of Light

If Broadcom is the "copper king," Marvell is the future "fiber optic king."

With the emergence of giant racks like NVIDIA NVL72, the distance between racks increases, rendering copper cables ineffective (due to high resistance), thus necessitating optical transmission.

1. Core Technology: DSP (Digital Signal Processor) — The Signal Plastic Surgeon

This is the crown jewel Marvell acquired after merging with Inphi.

Chaos of Optical-to-Electrical Conversion: When an optical signal travels hundreds of meters through a fiber optic cable and is then converted back to an electrical signal, its waveform is often degraded (full of noise, blurry).

Simple Analogy: Restoring a blurry old photo.

The received signal is like a water-damaged, blurry photograph. The DSP chip is an ultra-high-speed AI photo editor. It performs 800 billion operations per second, accurately reconstructing from a pile of noise: "Ah, this is a 1, and that is a 0."

Strategic Importance: In an 800G optical transceiver module, this DSP chip is the most expensive and critical component.

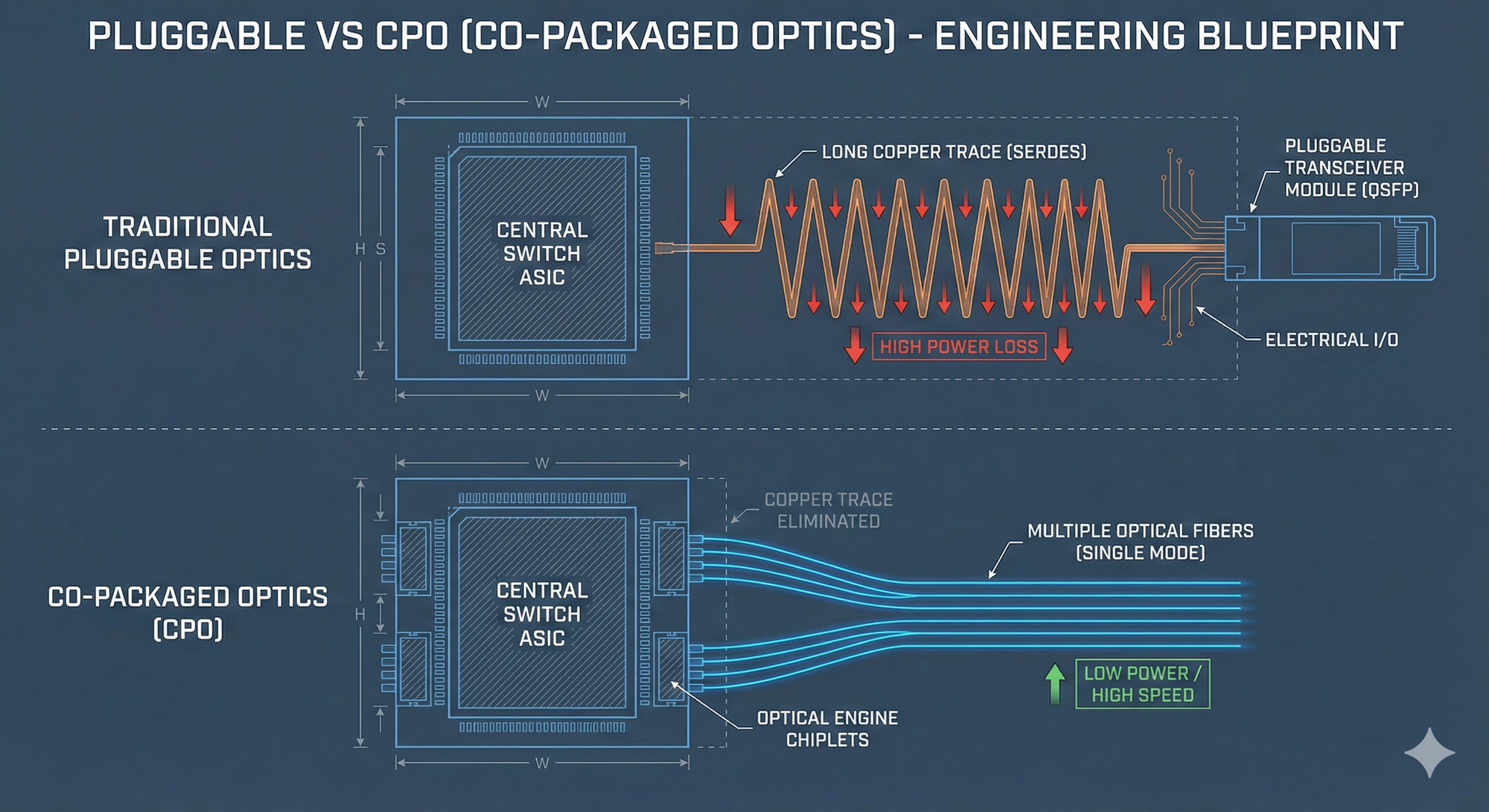

2. Future Trend: CPO (Co-Packaged Optics) — Plugging Fiber Optics Directly into the Chip

This is the next holy grail of the semiconductor industry, and Marvell has the deepest penetration here.

Current State (Pluggable): Fiber optic cables are plugged into optical modules at the back of the server, and the signal has to travel a long stretch of copper wire to reach the GPU. This copper segment consumes a lot of power.

Future (CPO): Direct access right into the chip.

We package the optical engine directly next to (or even on top of) the GPU. Optical signals travel directly into the chip via an "elevator," eliminating the need for that power-hungry copper pathway. Marvell is developing this technology for AWS and NVIDIA; it's the ultimate solution to AI's power consumption problem.

3. ASIC Strategy: AWS's Arsenal

Marvell has replicated Broadcom's model, but its major anchor client is Amazon (AWS).

Projects: Trainium (Training) & Inferentia (Inference)

AWS's chips focus on "connectivity." Because AWS's cloud architecture is enormous, chips must jump between tens of thousands of servers. Marvell provides the strongest Ethernet Switch IP and Optical PHY IP, ensuring AWS's chips transmit data seamlessly within the cloud.

🏗️ Chapter Three: Deep Dive into the ASIC Business Model (The Why)

Why are software companies like Google, AWS, Meta, and Microsoft suddenly developing their own hardware? What is the economics behind this trend?

1. General-Purpose vs. Custom: Swiss Army Knife vs. Scalpel

NVIDIA H100 (General-Purpose): Swiss Army Knife

It needs to do everything: FP64 (scientific computing), FP32 (graphics), INT8 (inference).

Cost: The chip is large, and half of its circuitry might never be used (Dark Silicon). You're paying for an entire Swiss Army knife, but only using its scissors.

Google TPU (Custom): Scalpel

Google found that 90% of its AI models perform "matrix multiplication." Therefore, TPUs eliminate all irrelevant circuits (such as ray tracing, graphics rendering), retaining only the matrix computation units.

Result: The chip area is half that of a GPU, power consumption is one-third, but it performs just as fast when running Google's workloads.

2. Why are Broadcom/Marvell Needed? (Can't They Do It Themselves?)

Google has the smartest mathematicians in the world, so why don't they complete the entire chip themselves?

Simple Analogy: The pitfalls of building your own house from scratch.

Google's mathematicians can draw "room layouts" (algorithm logic). However, for a chip to function, it also needs a "foundation," "plumbing and electricity," "external roads," and a "security system" (these are called Interface IPs).

SerDes Barrier: Developing a SerDes interface capable of 112G speeds requires analog circuit experts 10 years. Google doesn't have such personnel (this is black magic).

Conclusion: Google found that buying off-the-shelf plumbing and electrical wiring IP from Broadcom is far cheaper than developing it from scratch, and it guarantees no leaks.

📊 Strategic Summary and Investment Perspective

What does this report tell us?

ASIC is MediaTek's Opportunity

Understanding what Broadcom does for Google (providing SerDes and packaging services) helps you understand what MediaTek is doing.

- MediaTek also has strong SerDes capabilities (from its networking division).

- MediaTek also has CoWoS capacity (TSMC VIP).

- MediaTek is cheaper than Broadcom and more compliant.

This is why Google and Meta have started discussions with MediaTek. While Broadcom is feasting, MediaTek is vying for a share, even aiming to take a bite out of the main course.

In-depth Research · Quantitative Perspective

Want more semiconductor quantitative research insights?

[Insight Subscription Plan] Bid Farewell to Retail Investor Mentality: Build Your Alpha Trading System with "Quantitative Chips" and "Consensus Data"EDGE Semiconductor Research

📍 Series Map — Navigate the Complete EDGE Semiconductor Research →